2022-10-11

为向广大科技工作者介绍中国电子与信息科学领域内的新理论、新思想、新技术,学会公众微信号特开设“CIE最前沿”栏目,定期展示学会期刊刊发的具有国内外先进水平的最新研究成果和技术进展。

磁性随机存取存储器(MRAM)作为一种新兴的非易失性存储器,较先有的闪存、SRAM等存储介质优势明显,因此吸引了TSMC、SAMSUNG、GlobalFoundries等国际大厂积极布局。自旋轨道矩MRAM(SOT-MRAM)又是该领域的前沿热点,目前在整个业界依然面临巨大挑战。本文作者通过一系列工艺改进最终成功制备了8英寸晶圆级可实现无场翻转的高性能SOT-MRAM器件,并对器件的磁学和电学性能(单器件和晶圆级)进行了系统的测试。器件各项指标与台积电2022年7月在VLSI会议上报道的8 Kb SOT-MRAM器件性能相当,处于国际领先水平。

论文信息:

Integration of high-performance spin-orbit torque MRAM devices by 200-mm-wafer manufacturing platform

Hongchao Zhang, Xiangyue Ma, Chuanpeng Jiang, Jialiang Yin, Shuqin Lyu, Shiyang Lu, Xiantao Shang, Bowen Man, Cong Zhang, Dandan Li, Shuhui Li, Wenjing Chen, Hongxi Liu, Gefei Wang, Kaihua Cao, Zhaohao Wang, Weisheng Zhao

J. Semicond, 2022, 43(10): 102501.

doi: 10.1088/1674-4926/43/10/102501

内容简介

北京航空航天大学赵巍胜教授和曹凯华助理教授课题组与致真存储(北京)科技有限公司研发团队合作在自旋轨道矩MRAM器件方面取得重要进展,相关研究结果以“利用200 mm晶圆工艺平台集成制备的高性能自旋轨道矩MRAM器件”(Integration of high-performance spin-orbit torque MRAM devices by 200-mm-wafer manufacturing platform)为题,将作为封面文章在Journal of Semiconductors (《半导体学报》) 2022年第10期发表。

磁性随机存取存储器(MRAM)作为一种新兴的非易失性存储器,具有高读写速度、高续航能力、长存储时间和低功耗等特点。近年来TSMC、SAMSUNG、GlobalFoundries等大型半导体厂商也在MRAM领域积极布局。一方面传统的嵌入式闪存(e-flash)是基于先擦除后写入的方式,每个擦写单元的擦除次数有限,会因为擦除次数过多而被磨损,进而影响整个e-flash的生命周期,同时e-flash在28 nm CMOS技术节点以下成本过高。相比之下MRAM具有可实现近乎无限次写入的优势,成本较低,因此,MRAM成为替代e-flash的重要解决方案。另一方面,MRAM也可替代SRAM以解决先进CMOS节点的潜在漏电问题。然而,目前比较成熟的Toggle-MRAM和自旋转移矩MRAM(STT-MRAM),由于写入速度限制和可靠性问题,很难取代L1或L2缓存。为了解决以上问题,研究人员提出了在三端器件中读写路径分离的自旋轨道矩MRAM(SOT-MRAM),从本质上解决了高写入电流导致的读错误和隧道结老化问题。

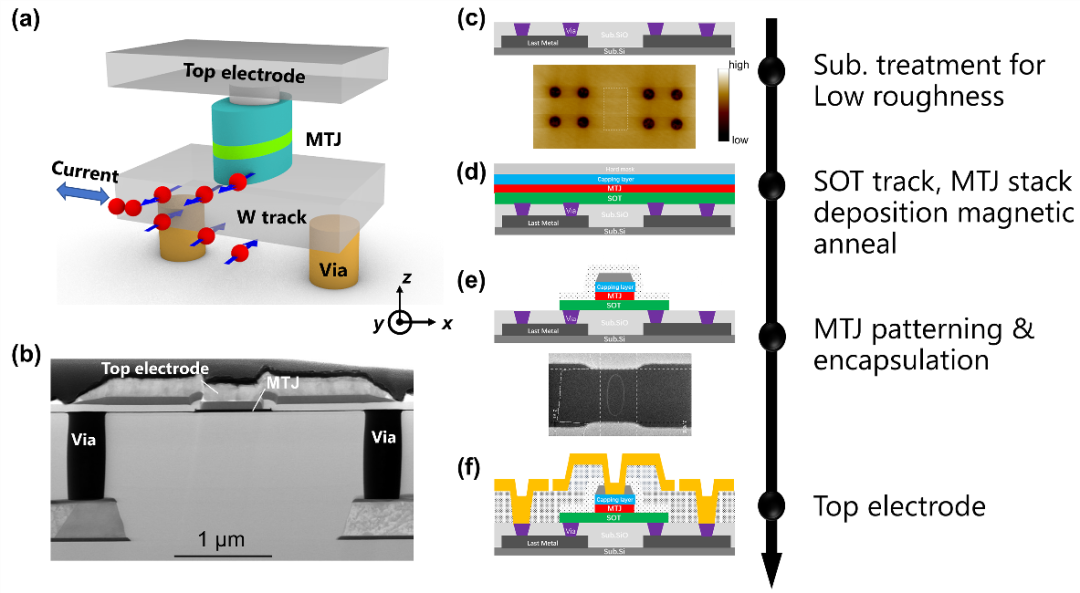

图1. SOT-MRAM器件结构及工艺流程图。

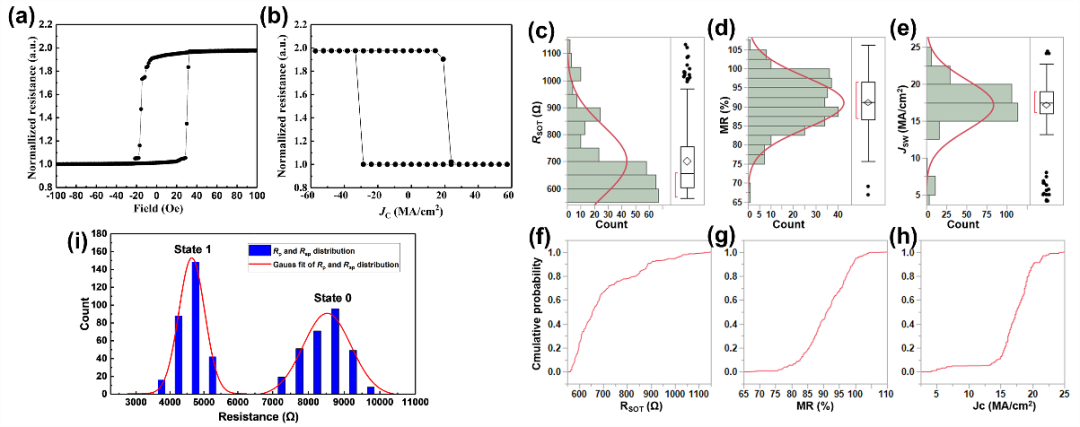

针对上述挑战,本工作通过调整BEOL工艺后衬底的粗糙度,成功实现了BEOL与SOT-MTJ器件的集成,并通过调整刻蚀工艺参数使得MTJ刻蚀精准停止在底电极层,保证了晶圆内器件的短路率低于5%,同时刻蚀对MTJ的损伤较小。最终成功制备了8英寸晶圆级可实现无场翻转的高性能SOT-MRAM器件,并对器件的磁学和电学性能(单器件和晶圆级)进行了系统的测试。器件各项指标与台积电2022年7月在VLSI会议上报道的8 Kb SOT-MRAM器件性能相当,在国内外处于领先地位。具体的,本工作首先测试了单器件的磁学和电学性能,在R-H和R-V测试中,器件TMR达到100%;晶圆级器件性能的均匀性RSOT sigma ~ 18%,TMR sigma ~ 7%,JSW sigma ~ 20%;器件短路率小于5%,Rap和Rp阻值间距~ 5 Rp sigma,满足存储器对器件的读写要求。在改变MTJ长轴大小时,发现器件翻转电流随长轴增大而逐渐增大,利用分流模型成功解释了器件翻转电流和MTJ尺寸的依赖关系。同时测试了器件翻转电流与电流脉宽之间的依赖关系,得到器件的原始翻转电流JC0 ~±38 MA/cm2;在器件的耐久性测试中,写入1010次电流后,测试器件底电极电阻、P态电阻和AP态电阻变化小于1%,具有良好的耐久性;利用磁场测得器件的热稳定因子Δ ~ 100,退火方法测试器件在工作温度85 ℃下的热稳定因子Δ ~ 55,以上结果均表明流片的器件满足十年期的存储要求。

图2. SOT-MRAM器件的电学和磁学性能测试;晶圆级RSOT、MR、JSW分布图和相应的CDF曲线;P态和AP态阻值的分布图。

博士生张洪超为该研究论文的第一作者,曹凯华助理教授、王戈飞博士、刘宏喜博士为通讯作者。该论文得到了国家重点科技研发计划和国家自然科学基金项目等支持。

文章PDF(点击标题即可下载):

曹凯华 ,助理教授,硕士生导师,北京航空航天大学集成电路科学与工程学院助理教授,青岛微电子研究院院长助理.

负责北航青岛研究院8英寸自旋芯片后道工艺平台,长期从事磁随机存储器核心器件制备工艺研究,完成国内首个兼容CMOS工艺的80 nm磁性隧道结器件制备及测试,首次实验验证了一种基于STT-MTJ搭建的单周期“与或非”存算一体器件。作为MRAM项目研发主要技术骨干,设计并开发了一整套磁性隧道结器件制备工艺,可支持亚40 nm磁隧道结器件的制备及全8英寸STT/SOT-MRAM研发;设计并搭建了一系列磁隧道结电磁输运特性表征设备及标准,完成各类自旋器件亚纳秒超快磁矩翻转测试。

刘宏喜,博士,致真存储(北京)科技有限公司首席技术官。

2012年于日本北海道大学获得电气及电子工程学博士学位,同年在北海道大学从事博士后研究工作;2013-2015年在法国Spin-TEC从事博士后研究工作;2015-2021年在美国格罗方德作为1Gb STT-MRAM项目技术团队核心成员从事MRAM的研发工作;该芯片现为世界上容量最大的产品级磁性存储器。2021年加入致真存储,作为首席技术官负责SOT-MRAM的研发。长期从事自旋电子学器件研究,有丰富的产业化经验,对磁隧道结器件的制备工艺有深入了解。

王戈飞,博士,致真存储(北京)科技有限公司首席执行官。

王戈飞(通讯作者)博士,致真存储(北京)科技有限公司首席执行官。2019年毕业于法国巴黎萨克雷大学,获得物理学博士学位,主要研究方向为自旋电子学。同年入站北京航空航天大学博士后流动站,主要进行磁性随机存储芯片(MRAM)的研发工作,并推动该研究成果进入产业化发展。2020年,参选人创办致真存储(北京)科技有限公司,大力组建高水平研发团队,建立公司内部研发组织架构。同年度公司申请了北京市中关村设立的“中关村颠覆性技术研发和成果转化”项目,在众多公司中脱颖而出,技术方案得到了专家的高度认可。

张洪超,北京航空航天大学2020级博士研究生。

(来源:半导体学报)

扫描二维码关注

中国电子学会公众号

扫描二维码加入

中国电子学会会员

第十九届电子年会|基础模型与通感信息处理专题论坛成功举办

第十九届电子年会|复杂网络时敏感知专题论坛成功举办

中国电子学会雷达分会首场青年科学家走进高校活动在武汉大学成功举办

第十九届电子年会|脑机智能交互前沿专题论坛成功举办

中国电子学会雷达分会第十一届委员会第四次工作会议在武汉召开

第十九届电子年会|智慧交通信息工程专题论坛成功举办

第十九届电子年会|“工业边缘智能专题论坛”成功举办

第十九届电子年会 | 先进无线通信技术与测试验证专题论坛在武汉召开